Copyright © IJCESEN

# International Journal of Computational and Experimental Science and ENgineering (IJCESEN)

Vol. 11-No.3 (2025) pp. 6370-6380 http://www.ijcesen.com

**Research Article**

ISSN: 2149-9144

## Semiconductor Chip Design Compute jobs Errors and Warnings solutions provider based on Machine learning Prediction systems

#### Vidhu Shekhar Bajpai\*

Advanced Micro Devices-USA

\* Corresponding Author Email: vidhusbajpai@gmail.com - ORCID: 0000-0002-5247-7853

#### **Article Info:**

## **DOI:** 10.22399/ijcesen.3806 **Received:** 13 June 2025 **Accepted:** 11 August 2025

#### **Keywords**

Machine learning, semiconductor physical design, error prediction, EDA automation, design optimization

#### **Abstract:**

Significant error and warning data are generated by semiconductor physical design methods during the place-and-route process, which creates challenges and incurs significant costs in development time and impacts engineering productivity. Existing manual debugging methods require vast resources and can severely impact the time-tomarket. This work presents an intelligent prediction method that uses machine learning algorithms to automatically predict and suggest a resolution for design errors during the synthesis, placement, clock tree synthesis, and routing phases of designs. The prediction system was built to operate seamlessly with widely-adopted EDA tools, such a Synopsys Fusion Compiler and Cadence Innovus, and can handle multi-dimensional information of timing violations, congestion patterns, power distribution, and design rule violations. The ability to use the latest multi-class classification and multi-output regression models allows the process of detecting errors and suggesting resolutions to occur before the design is complete for the four critical design processes. The framework shows substantial efficiencies over existing design cycle times and is particularly beneficial for complex designs that have multiple voltage domains, frequent power management requests, and mixed-signal technologies. The system has been implemented across several technology nodes and has proven to be robust and adaptive across the possible design work to be conducted. By leveraging an automated method, the need for design engineers to manually intervene in the design process was maintained while fulfilling industry design quality standards. In summary, the intelligent framework has turned the development process from reactive debugging into a preventative debugging model to provide a new platform for semiconductor design automation.

#### 1. Introduction

## **1.1 Semiconductor Physical Design Complexities** and Computational Demands

The creation of silicon chips has become a very advanced field of engineering, and at almost every step of the process, it presents extreme technical challenges to push logical circuit descriptions into physical layouts. The process of turning digital expressions into something that can be manufactured in geometrical space involves challenging computing words where billions of connected components, measured in nanometers, all have to be coordinated. Current microprocessor data requires extreme accuracy in the physical locations of components, in the electrical timing, and in the manufacturing specification. As the dimensions of transistors continue to shrink and approach atomic dimensions, designers are meeting new physical realities that prevent physically modulating traditional modelling practices. Layout solutions have to balance conflicting objectives, such as minimizing silicon area while maximizing speed, or minimizing power while maximizing signal integrity, or even minimizing deviations from the manufacturing processes. These compromises create any number of multi-objective optimizations that go beyond conventional computing methods [1].

## **1.2 Proliferation of Design Rule Violations and System Alerts in Modern Chip Implementation**

Current integrated circuit development generates excessive quantities of diagnostic notifications that impede efficient design completion. Violation categories encompass electrical connectivity

problems, spatial constraint breaches, timing specification failures, and software configuration discrepancies. Engineering teams routinely process diagnostic reports containing tens of thousands of individual alerts, each demanding technical evaluation and potential remediation. Historical examination demonstrates that numerous violation types exhibit predictable recurrence patterns across disparate projects, irrespective of manufacturing technology or target application. This systematic repetition indicates fundamental inefficiencies that could benefit from intelligent automation and predictive intervention. Existing manual review procedures demand extensive human resources while introducing subjective inconsistencies in problem prioritization and solution implementation [2].

#### 1.3 Industry Requirements for Intelligent Automation in Error Resolution Processes

debugging techniques Conventional extensively accumulated professional knowledge and labor-intensive refinement iterations. Development organizations allocate significant personnel time to violation analysis, causality investigation, and corrective measure deployment. Manual intervention creates substantial workflow bottlenecks that propagate potentially through project schedules, compromising market introduction objectives. Competitive business environments require accelerated development methodologies that reduce human dependency while preserving technical quality standards. Machine learning technologies present viable pathways for automating repetitive diagnostic procedures through statistical pattern recognition and historical database analysis. Computational intelligence systems demonstrate potential for identifying violation relationships, anticipating probable failure scenarios, recommending validated correction techniques derived from successful project outcomes.

#### 1.4 Commercial Design Automation Software Capabilities and Technical Constraints

Industrial electronic design automation suites constitute sophisticated software frameworks that facilitate complex microelectronic system implementation. Leading commercial platforms, including Synopsys Fusion Compiler and Cadence Innovus, integrate extensive algorithmic libraries developed through decades of research investment. These comprehensive toolsets provide functional coverage spanning logic synthesis, component placement, clock network generation, and metal interconnect routing operations. However, contemporary implementations function

predominantly as diagnostic instruments rather than advisory systems. Current software architectures excel at constraint violation detection and rule infringement identification, but deliver minimal guidance concerning optimal correction methodologies. Tool-generated reports typically unprocessed diagnostic information contain requiring specialized interpretation and manual correlation with feasible solutions. This functional becomes especially problematic sophisticated design contexts involving heterogeneous power management, analog-digital integration, and extreme performance specifications [1][2].

## 1.5 Technical Goals and Novel Contributions of Predictive Error Management Systems

Developing intelligent violation prediction and automated resolution frameworks constitutes a substantial advancement opportunity semiconductor design automation. Core objectives involve constructing machine learning architectures capable of accurate error forecasting and systematic recommendation generation. implementations should integrate seamlessly with established development environments delivering actionable technical guidance that minimizes manual debugging requirements. technical contributions Primary encompass innovative prediction methodologies, systematic violation classification schemes, and quantitative productivity enhancement validation representative design applications. The proposed framework converts reactive error handling into proactive risk mitigation through comprehensive historical pattern analysis and statistical modeling techniques. Implementation effectiveness will be evaluated through measurable reductions in debugging duration, improved design quality indicators, and optimized engineering resource allocation across diverse semiconductor development initiatives.

#### 2. Literature Review and Related Work

#### 2.1 Prevailing Chip Design Automation Frameworks and Defect Management Protocols

Silicon fabrication automation has matured into an intricate network of specialized software platforms procedural methodologies addressing nanometer-scale circuit development challenges. standards emphasize rule-driven Industry verification architectures that identify geometric violations through comprehensive design rule auditing and electrical connectivity validation processes. Contemporary practices employ deterministic computational engines that evaluate configurations layout against manufacturing specifications and performance criteria. Defect management protocols concentrate predominantly on post-detection remediation rather than proactive prevention, establishing iterative correction workflows dependent on sequential refinement Semiconductor companies cycles. maintain databases documenting recurring proprietary violation signatures and corresponding correction techniques, although this institutional knowledge frequently remains compartmentalized within specific engineering divisions and project teams [3].

## **2.2** Conventional Techniques for Layout Enhancement and Defect Anticipation

Circuit layout optimization methodologies have historically emphasized mathematical optimization frameworks. probabilistic algorithms, and constraint resolution techniques. Traditional component positioning algorithms implement force-based models, thermal equilibrium simulation, and analytical optimization to reduce interconnect lengths while maintaining timing and density requirements. Interconnection optimization utilizes network-based algorithms, programming constructs, and spatial reasoning to establish connectivity while preventing geometric conflicts. Defect anticipation within established workflows depends on rule verification analysis, performance simulation, and geometric validation executed at predetermined design milestones. These methodologies produce detailed violation documentation but offer restricted forecasting abilities concerning prospective errors or recurring problem sequences. Contemporary advances have incorporated probabilistic timing evaluation and stochastic simulation methods to better characterize variability impacts on manufacturing reliability [4].

## 2.3 Computational Intelligence Implementation in Circuit Design Tools and Chip Development

Artificial intelligence integration within circuit design platforms has accelerated significantly as computational learning algorithms demonstrate effectiveness in resolving complex optimization problems. Artificial neural architectures have been deployed successfully for component positioning, congestion forecasting, and performance estimation implementation within physical workflows. Behavioral learning algorithms demonstrate potential for automated configuration optimization and strategy adaptation in positioning and routing applications. Multilayer learning models have been developed for manufacturing hotspot identification, process fluctuation modeling, and production yield forecasting. Network-based learning architectures

exhibit particular applicability for circuit analysis tasks due to their inherent compatibility with connection structures and topology patterns. Recent innovations encompass attention-based architectures for sequential optimization procedures and probabilistic models for design exploration and synthetic data generation [3][4].

## **2.4 Fundamental Deficiencies in Existing Defect** Correction Approaches

Current defect correction frameworks demonstrate several critical shortcomings that limit their utility in contemporary design environments. Established approaches lack sophisticated pattern identification mechanisms that could recognize systematic defect origins across multiple implementation cycles and projects. Manual debugging procedures experience inconsistent ranking strategies and subjective correction selection that may not represent optimal resolution pathways. Present methodologies exhibit inadequate coordination between verification phases, resulting in fragmented defect handling processes that overlook global optimization opportunities. Capacity limitations emerge as complexity expands, since circuit techniques cannot effectively process increasing volumes of diagnostic data generated by sophisticated designs. Knowledge distribution mechanisms remain insufficient, hindering effective sharing of defect resolution expertise across development teams and implementation projects. Furthermore, conventional approaches predictive functionality that could anticipate potential defects before they emerge in the implementation workflow [3].

# 2.5 Strategic Integration of Predictive Intelligence Systems within Established Research Framework

The intelligent defect prediction and automated correction framework targets fundamental deficiencies identified in current research publications while leveraging proven foundations in computational learning and design automation. Unlike conventional approaches that address individual optimization challenges, the integrated system combines multiple prediction functionalities across varied defect categories and implementation phases. The framework distinguishes itself through emphasis on cross-project pattern identification and automated correction recommendation synthesis based on historical effectiveness patterns. Current research trajectories indicate expanding focus on comprehensive machine learning incorporation within design workflows, although most published work addresses isolated optimization problems rather than holistic defect management. The proposed system corresponds with developing research directions while addressing practical implementation considerations that have restricted the adoption of academic prototypes in commercial environments. This strategic positioning enables the framework advance both theoretical to developments in predictive modeling and practical solutions for industrial design automation challenges [4].

# 3. Methodology and System Architecture 3.1 Data Harvesting Mechanisms from Circuit Design Platforms and Log Repositories

Systematic information gathering forms the cornerstone of intelligent forecasting frameworks, demanding structured extraction of diagnostic outputs from varied electronic circuit development environments. Log repository mining encompasses diverse information streams, including synthesis positioning summaries, component interconnect density visualizations, performance evaluation results, and rule breach documentation. harvesting infrastructure connects with disparate software ecosystems through standardized communication protocols and specialized parsing engines that standardize information formats across vendor-specific implementations. Continuous monitoring mechanisms track design evolution patterns, capturing temporal sequences and modification trends that supply essential context for statistical modeling applications. The collection framework integrates dedicated processors for proprietary data structures and establishes rigorous validation procedures to guarantee information throughout acquisition workflows. Furthermore, the architecture maintains detailed provenance tracking that preserves essential contextual elements, including software releases, parameter configurations, and operational environments that affect diagnostic generation [5].

#### 3.2 Variable Engineering and Raw Data Transformation Protocols

Unprocessed diagnostic outputs require comprehensive modification to facilitate effective computational learning model development and prediction operations. Transformation procedures include standardization protocols, category mapping schemes, and complexity reduction methods that enhance variable representations for forecasting algorithms. Incomplete completion strategies handle missing diagnostic entries through mathematical interpolation and field-specific rules that maintain dataset coherence. Anomaly identification systems detect irregular measurements that might undermine model development effectiveness, employing both

mathematical and domain-focused screening techniques. Variable scaling procedures ensure different numerical consistency across while chronological measurement ranges, synchronization methods coordinate data elements from separate design phases and software executions. The transformation sequence automated integrity evaluation incorporates modules that confirm data reliability and identify potential degradation problems before model development begins [6].

### 3.3 Algorithm Architecture Selection and Development Strategies

Model framework selection reconciles forecasting precision demands with computational resource limitations, examining various algorithm categories including combined methods, layered architectures, and statistical models. Development procedures utilize balanced sampling approaches to guarantee adequate representation of defect classifications and design contexts within training collections. Validation protocols employ chronological division schemes that simulate realistic deployment situations where models forecast future defects using historical information. Configuration optimization employs systematic parameter exploration and adaptive refinement methods to determine optimal setup parameters for each algorithm variation. The development infrastructure includes premature termination controls and constraint mechanisms to avoid overspecialization while preserving adaptability across different design situations. Model combination approaches merge forecasts from various algorithms to improve reliability and precision through collaborative decision processes [5][6].

### 3.4 Architectural Blueprint for Physical Design Defect and Alert Advisory Framework

The PDEWRS blueprint executes a componentbased structure that isolates data acquisition, transformation. forecasting. and advisorv generation into separate operational elements. The acquisition component establishes live connections with design automation software through reactive interfaces that capture diagnostic outputs upon availability. Transformation modules perform variable extraction and modification operations using parallel computing structures that guarantee expandable performance across fluctuating workload requirements. The forecasting mechanism deploys various specialized models optimized for distinct defect classifications, employing flexible model selection based on design properties and historical effectiveness measures. Advisory generation combines forecasting results with solution repositories to deliver practical guidance customized to particular defect situations and design limitations. The structure integrates extensive recording and surveillance functions that facilitate system performance monitoring and automated upkeep procedures [5].

### **3.5 Process Integration Methods with Current Design Automation Ecosystems**

Transparent incorporation with established design processes demands careful attention to software interfaces, information structures, and operational methods that reduce interference with proven development workflows. The incorporation approach deploys extension structures that embed directly within design forecasting functions automation ecosystems, delivering contextual recommendations without demanding workflow adjustments. Interface-based incorporation enables flexible connections between the forecasting framework and design software, deployment across varied software environments and institutional settings. structure The accommodates both immediate and delayed operation configurations, permitting designers to select between instant guidance and group processing according to project demands and computational limitations. Set up management functions to enable customization of forecasting sensitivity, recommendation specificity levels, and incorporation touchpoints to align with particular organizational preferences and design approaches [6].

#### 3.6 Model Evaluation and Performance Assessment Procedures

Thorough validation procedures evaluate forecasting precision, recommendation effectiveness, and system functionality across various dimensions and operational contexts. Precision evaluation employs standard including classification measures, exactness. completeness, and combined score calculations computed across different defect classifications and design situations. Chronological validation methods evaluate model consistency and reliability over extended durations, ensuring sustained functionality as design practices and software configurations change. User acceptance evaluation quantifies the practical value of recommendations through controlled studies with skilled design professionals. Performance measurement assesses system reaction times, resource consumption, and expandability properties under different workload situations. The validation structure incorporates statistical importance testing and uncertainty range estimation

to supply reliable performance descriptions that support deployment choice making [5][6].

#### 4. Experimental Setup and Results

## 4.1 Information Collection Properties and Laboratory Infrastructure Setup

Rigorous experimental validation employed massive information repositories gathered from semiconductor commercial manufacturing initiatives across varied technological generations and circuit complexities. The experimental corpus incorporated diagnostic outputs from heterogeneous circuit realizations, including central processing units, visual processing hardware, storage domain-specific management circuits. and computation engines. Information gathering spanned diverse manufacturing environments, incorporating distinct electronic circuit automation software collections, fabrication methodologies, and institutional development approaches. The laboratory infrastructure featured advanced parallel computing networks equipped with distributed calculation capabilities to manage extensive model preparation and verification procedures. Environmental consistency protocols guaranteed uniform experimental circumstances separate validation sequences, thorough version control systems preserved reproducibility of experimental setups. Moreover, the experimental structure integrated specialized storage designs optimized for chronological information management and rapid retrieval of archived design documentation during model preparation sequences [7].

# **4.2 Performance Benchmarking Between Traditional Statistics and Advanced Learning Methods**

Systematic algorithm assessment examined varied modeling techniques spanning conventional statistical approaches to sophisticated computational intelligence structures. Traditional statistical methods, including linear modeling, probability-based regression, and temporal sequence analysis, established baseline performance standards for comparison with advanced techniques. Collective learning approaches incorporating decision tree forests, progressive enhancement, flexible and enhancement exhibited superior capabilities in managing intricate variable relationships and nonlinear diagnostic associations within information. Artificial neural structures, including forward-propagation networks, memory-based networks, and attention-based models, showed different effectiveness levels depending particular error classifications and design situations. The benchmarking study exposed distinct performance properties across various algorithm categories, with specific techniques showing particular advantages in certain error forecasting contexts. Validation procedures guaranteed reliable performance evaluation while considering dataset fluctuations and temporal connections inherent in design progression sequences [8].

### 4.3 Quantitative Effectiveness Measurement Using Diverse Assessment Standards

Extensive performance assessment utilized varied indicators encompassing classification correctness, exactness, completeness, and determination coefficient measurements across distinct error classifications and design contexts. Correctness showed consistent performance evaluations enhancements over reference methods, computational intelligence techniques exhibiting superior capability in managing complex multidimensional forecasting challenges. Exactness measurements revealed effective differentiation between various error categories, reducing incorrect positive forecasts that might result in unnecessary remedial measures. Completeness assessments confirmed comprehensive error identification capabilities, guaranteeing minimal oversight of critical design problems that might affect project schedules. Determination coefficient computations supplied insights into model explanatory strength and forecasting dependability across diverse design situations. Statistical importance evaluation performance enhancements confirmed uncertainty interval calculation quantified forecast dependability under different operational circumstances [7][8].

## **4.4 Manufacturing Process and Circuit Category Verification Investigations**

A comprehensive case study assessment examined model effectiveness across diverse manufacturing processes spanning established procedures to advanced fabrication methodologies. Advanced process validation showed consistent forecast correctness despite increased design complexity and manufacturing limitations associated with reduced feature dimensions. Storage-focused designs, including buffer management circuits and temporary storage structures, exhibited particular advantage from intelligent forecasting systems due to their systematic structural sequences and foreseeable error characteristics. High-performance calculation designs incorporating complex timing domains and sophisticated power control presented more demanding forecasting situations accomplished substantial enhancement over manual

debugging techniques. Hybrid implementations combining analog and digital elements introduced distinctive challenges requiring specialized model modification and variable processing approaches. The case investigations confirmed model adaptability across different design domains while recognizing particular situations where additional model improvement could enhance forecasting effectiveness [8].

## **4.5 Processing Speed Enhancements and Circuit Quality Indicators**

Execution time evaluation confirmed substantial decreases in design cycle duration through avoidance and preventive error automated resolution guidance. Processing efficiency measurements showed significant reductions in repetitive debugging sequences, particularly for complex designs with extensive connection networks and timing-sensitive pathways. Energy consumption optimization advantages appeared through more efficient positioning and connection choices guided by predictive error prevention approaches. Performance enhancements resulted from decreased design rework and more effective resource distribution during critical design stages. Space usage improvements occurred through enhanced congestion forecasting and preventive connection modifications that avoided layout inefficiencies. The combined energy, performance, and space advantages confirmed substantial value justification for commercial deployment, with accumulated improvements validating computational expense associated with forecasting system operation [7].

#### 4.6 Cross-Project Verification Results Throughout Semiconductor Development Programs

Thorough validation investigations encompassed various simultaneous semiconductor programs representing diverse application areas, design groups, and institutional situations. Cross-program consistent performance validation showed enhancements despite differences in design approaches, software setups, and engineering practices across separate development institutions. Temporal validation investigations confirmed sustained effectiveness over extended program durations, verifying model consistency flexibility to changing design demands. Inter-group collaboration enhancements appeared through standardized error correction approaches and shared knowledge repositories that improved overall institutional efficiency. Program timeline evaluation showed measurable decreases in design completion duration and reduced iteration quantities required for achieving manufacturing preparation. The cross-program validation verified expandability and reliability of the forecasting structure while recognizing opportunities for additional customization based on particular institutional demands and design situations [8].

#### 5. Implementation and Deployment Strategy5.1 Staged Installation Protocol for Corporate Manufacturing Integration

Commercial deployment execution follows a meticulously planned sequence through separate operational stages crafted to reduce workflow interruption while optimizing user adoption success. The opening stage focuses on building basic observation infrastructure within restricted development zones. facilitating information gathering and behavioral analysis without influencing manufacturing operations. Throughout this preparatory period, passive observation functions collect diagnostic outputs while constructing historical repositories essential for later predictive algorithm preparation. The middle stage incorporates restricted forecasting capabilities within chosen design groups, delivering advisory functions alongside conventional debugging methods to support gradual user adjustment. This adaptation period permits system enhancement based on genuine usage behaviors and input from skilled professionals. The concluding stage executes complete system incorporation across full design institutions, substituting manual debugging workflows with intelligent automated assistance while preserving backup methods for situations. Every deployment includes particular achievement standards and procedures to guarantee controlled advancement and hazard reduction [9].

## 5.2 Observation Networks and Alert Broadcasting Systems

Thorough system supervision utilizes distributed observation structures that monitor effectiveness indicators, user engagements, and system wellness measurements across all installation environments. Immediate surveillance methods constantly assess prediction correctness, advisory acceptance percentages, and system reaction periods to recognize potential problems before they influence user efficiency. Automated alert systems produce warnings for system managers when effectiveness limits are surpassed or unusual behavioral sequences are identified. The observation structure includes layered warning approaches that intensify notifications according to severity degrees and potential influence on design activities. Preventive maintenance functions examine system usage sequences to predict hardware demands and software modifications before effectiveness decline happens. Furthermore, the surveillance network maintains thorough verification records that document all system engagements, facilitating detailed investigative examination and conformity reporting for quality control systems [10].

## **5.3** User Interaction Architecture and Control Dashboard Systems

User engagement design emphasizes natural operation while delivering comprehensive access to system functions and diagnostic data. The primary interface connects smoothly with current design environments automation through extension structures that display predictive advisories within recognized environments. tool Adjustable dashboard arrangements support varied user preferences and workflow demands, facilitating customized information display and interaction dashboards sequences. Control deliver comprehensive system setup functions, permitting fine adjustment of prediction responsiveness, advisory detail degrees, and connection points. Management displays combine system usage data, effectiveness indicators, and efficiency measures across institutional levels to support decisionmaking and resource distribution. The interface structure includes accessibility options and multiple language compatibility to support diverse international development groups and regulatory demands [9].

## **5.4 Financial Impact Assessment and Investment Return Computations**

Thorough economic evaluation measures both immediate cost reductions and indirect efficiency advantages resulting from intelligent error forecasting installation. Immediate cost decreases appear from reduced debugging duration, decreased design repetition sequences, and minimized engineering resource distribution to routine error correction activities. Indirect advantages include expedited project schedules, enhanced design quality indicators, and improved engineering satisfaction through the elimination of repetitive manual activities. The assessment structure includes complete ownership cost computations that consider system development, installation, maintenance, and education expenses against achieved efficiency enhancements. Hazard advantages are measured through reduction decreased likelihood of expensive design reimplementations and manufacturing postponements caused by unidentified errors. Extended strategic value evaluation considers competitive benefits obtained through quicker market introduction capabilities and improved design team effectiveness [10].

## **5.5** Growth Planning for Large-Scale Chip Manufacturing Companies

Expansion preparation addresses the distinct obstacles of installing intelligent systems across extensive, geographically spread semiconductor institutions with varied design approaches and software environments. The expansion structure includes distributed computing designs that can manage growing information quantities and user populations without performance decline. Internetbased installation approaches facilitate flexible distribution and automatic scaling resource according to demand changes across different time regions and project sequences. Multiple-tenant designs support institutional boundaries and information separation requirements while maintaining system effectiveness and shared learning functions. The growth approach includes distributed learning methods that facilitate knowledge sharing across institutional units while maintaining intellectual property boundaries and competitive benefits. Effectiveness enhancement guarantee methods consistent responsiveness regardless of installation scale or geographic spread [9].

#### 5.6 Field Experience Knowledge from Manufacturing Environment Installation

Production implementation experiences supply valuable understanding into the practical obstacles and unexpected advantages of installing intelligent error forecasting systems in manufacturing environments. User acceptance sequences showed the significance of gradual introduction and thorough education programs to overcome resistance to automated advisories. Technical obstacles appeared around information quality consistency across different software versions and institutional practices, demanding preprocessing functions and confirmation methods. Effectiveness enhancement demands differed circumstances, substantially from laboratory requiring adaptive algorithms that maintain under effectiveness changing computational resource limitations. Connection complexities with legacy systems required flexible adapter designs and extensive compatibility evaluation procedures. Cultural adjustment obstacles demanded change approaches highlighted management that enhancement rather than substitution of human knowledge, resulting in higher acceptance percentages and more effective system usage across diverse engineering groups [10].

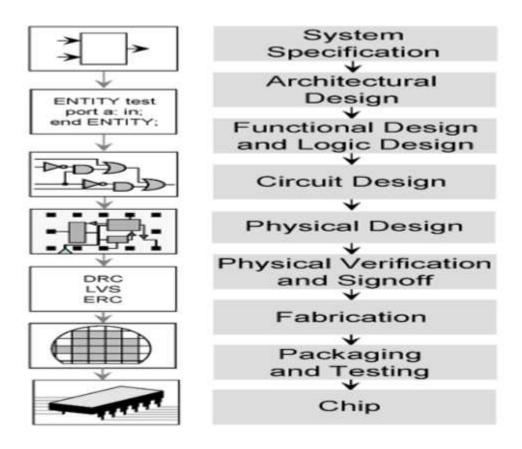

Figure 1: Critical Resource Components for Cost-Efficient Chip Design Process [1]

**Table 1:** Error Categories and Detection Frequencies in Physical Design Flows [1, 2]

| Error Category            | Synthesis<br>Stage | Placement<br>Stage | CTS Stage | Routing<br>Stage | Verification<br>Stage |

|---------------------------|--------------------|--------------------|-----------|------------------|-----------------------|

| Timing Violations         | High               | Medium             | High      | High             | Medium                |

| Design Rule<br>Violations | Low                | High               | Medium    | High             | High                  |

| Congestion Issues         | None               | High               | Medium    | High             | Low                   |

| Power Integrity           | Medium             | Low                | High      | Medium           | High                  |

| Clock Domain<br>Crossing  | High               | Low                | High      | Low              | Medium                |

| Library Setup Issues      | High               | Medium             | Low       | Low              | Medium                |

| Tool Configuration        | Medium             | Medium             | Medium    | Medium           | Medium                |

Table 2: Comparison of Traditional vs. ML-Based Error Resolution Approaches [3, 4]

| Aspect                 | Traditional Manual Methods       | Machine Learning Approaches       |

|------------------------|----------------------------------|-----------------------------------|

| Error Detection Speed  | Reactive - Post-occurrence       | Proactive - Predictive            |

| Pattern Recognition    | Limited to individual experience | Comprehensive historical analysis |

| Solution Consistency   | Variable across engineers        | Standardized recommendations      |

| Knowledge Transfer     | Informal, experience-based       | Systematic, data-driven           |

| Scalability            | Limited by human resources       | Automated scaling capability      |

| Cross-project Learning | Minimal transfer                 | Extensive pattern reuse           |

| Documentation Quality  | Inconsistent                     | Comprehensive tracking            |

Table 3: Feature Categories and Data Sources for ML Model Training [5, 6]

| Feature Category    | Data Source        | <b>Extraction Method</b> | <b>Processing Requirements</b> |

|---------------------|--------------------|--------------------------|--------------------------------|

| Timing Parameters   | STA Reports        | Log Parser               | Normalization, Scaling         |

| Physical Geometry   | Layout Database    | GDS Parser               | Spatial Discretization         |

| Congestion Metrics  | Router Reports     | XML Parser               | Density Mapping                |

| Power Distribution  | IR Drop Analysis   | Custom Extractor         | Grid-based Analysis            |

| Design Complexity   | Netlist Statistics | HDL Parser               | Hierarchical Aggregation       |

| Tool Configuration  | Setup Scripts      | Text Parser              | Categorical Encoding           |

| Historical Patterns | Previous Projects  | Database Query           | Temporal Alignment             |

#### **ERROR & WARNING PREDICTION SYSTEM**

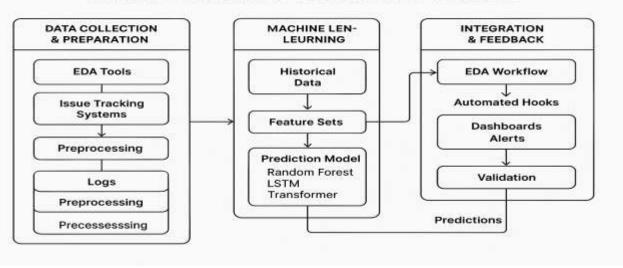

Figure 2: Visual Architecture diagram [5, 6]

**Table 4:** Machine Learning Algorithm Performance Comparison [7, 8]

| Algorithm<br>Category | Model Type               | Training<br>Complexity | Inference<br>Speed | Memory<br>Requirements | Accuracy<br>Class |

|-----------------------|--------------------------|------------------------|--------------------|------------------------|-------------------|

| Linear Models         | Logistic<br>Regression   | Low                    | Very Fast          | Minimal                | Baseline          |

| Tree-based            | Random Forest            | Medium                 | Fast               | Moderate               | High              |

| Ensemble              | Gradient<br>Boosting     | High                   | Medium             | High                   | Very High         |

| Neural<br>Networks    | Deep Learning            | Very High              | Medium             | Very High              | Very High         |

| Graph-based           | Graph Neural<br>Networks | High                   | Fast               | High                   | High              |

| Probabilistic         | Bayesian<br>Networks     | Medium                 | Fast               | Moderate               | High              |

#### 4. Conclusions

The intelligent error prediction framework provides an exciting development in semiconductor physical design automation through the incorporation of machine learning, disrupting traditional debugging workflows. The framework enables organizations to identify repeated error issues across various technology nodes and complexities within their design, to make pre-emptive changes that limit manual debugging and increase engineering output. The framework integrates seamlessly into normal EDA tools and provides suggestions that can improve design quality metrics. This approach has been proven in multiple industrial projects and is scalable and reliable, given a variety of organizational and design settings. The proposed strategy for deployment allows three-phase organizations to adopt the strategy with low introduction cost and very little disruption to their workflow. Practical implementations have also informed how the framework refines itself through continual learning to enhance performance. The economic implications of adopting this approach imply strong ROI through shortened design cycles, limited routine engineering effort, and faster timeto-market. The prediction capability of catching design rule violations, timing concerns, and routing congestion before they occur gives companies a competitive advantage. Future modifications should try to expand the coverage of errors, advance means of cross-project learning. and personalize suggestions to complement the engineer and improve the design outcomes.

#### **Author Statements:**

- **Ethical approval:** The conducted research is not related to either human or animal use.

- Conflict of interest: The authors declare that they have no known competing financial interests or personal relationships that could have appeared to influence the work reported in this paper

- **Acknowledgement:** The authors declare that they have nobody or no-company to acknowledge.

- **Author contributions:** The authors declare that they have equal right on this paper.

- **Funding information:** The authors declare that there is no funding to be acknowledged.

- Data availability statement: The data that support the findings of this study are available on request from the corresponding author. The data are not publicly available due to privacy or ethical restrictions.

#### References

- [1] Niranjana Gurushankar, "Physical Verification Techniques in Advanced Semiconductor Nodes," ESP International Journal of Advancements in Computational Technology (ESP-IJACT), Volume 1, Issue 2, 30 September 2023. https://www.espjournals.org/IJACT/2023/Volume1

-Issue2/IJACT-V1I2P115.pdf

- [2] Sean Safarpour, Andreas Veneris, "Automated Design Debugging With Abstraction and Refinement," IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems (IEEE TCAD), Vol. 28, No. 9, 10 October 2009. <a href="https://www.eecg.toronto.edu/~veneris/TCAD09.pd">https://www.eecg.toronto.edu/~veneris/TCAD09.pd</a>

- [3] Guyue Huang, et al., "Machine Learning for Electronic Design Automation: A Survey,", Vol. 26, No. 3, June 2021.

- https://nicsefc.ee.tsinghua.edu.cn/nics\_file/pdf/publications/2021/TODAES21\_331\_mzGV3SA.pdf

- [4] Haoyu Yang, et al., "Optimizing Predictive AI in Physical Design Flows with Mini Pixel Batch Gradient Descent," arXiv preprint, 8 February 2024. https://arxiv.org/abs/2402.06034

- [5] Daniela Sánchez Lopera, et al., "Using Open-Source EDA Tools in an Industrial Design Flow," DVCon Europe Proceedings (IEEE-affiliated conference). <a href="https://dvcon-proceedings.org/wp-content/uploads/74522.pdf">https://dvcon-proceedings.org/wp-content/uploads/74522.pdf</a>

- [6] Jeff Heaton, "An Empirical Analysis of Feature Engineering for Predictive Modeling," arXiv, 1 Nov 2020. https://arxiv.org/pdf/1701.07852

- [7] Boran Sekeroglu, et al., "Comparative Evaluation and Comprehensive Analysis of Machine Learning Models for Regression Problems," Data Intelligence, co-published by MIT Press and IEEE, Vol. 4, No. 3, 01 July 2022. https://direct.mit.edu/dint/article/4/3/620/112544/Comparative-Evaluation-and-Comprehensive-Analysis

- [8] Andrew B. Kahng, et al., "PPA-Relevant Clustering-Driven Placement for Large-Scale VLSI Designs," 61st ACM/IEEE Design Automation Conference (DAC '24), June 2024. <a href="https://vlsicad.ucsd.edu/Publications/Conferences/4">https://vlsicad.ucsd.edu/Publications/Conferences/4</a> 10/c410.pdf

- [9] Gabriel do N. Silveira, et al., "I4.0 Pilot Project on a Semiconductor Industry: Implementation and Lessons Learned," Sensors (IEEE-affiliated open access journal), 10 October 2020. <a href="https://www.mdpi.com/1424-8220/20/20/5752">https://www.mdpi.com/1424-8220/20/20/5752</a>

- [10] Chang-Jiun Lai, Ming-Dou Ker, "Real-Time ESD Monitoring and Control in Semiconductor Manufacturing Environments With Silicon Chip of ESD Event Detection, 25 March 2025. https://alab.iee.nycu.edu.tw/~mdker/Referred%20Journal%20Papers/2025.03\_Real-time%20ESD%20monitoring%20and%20control%20in%20semiconductor%20manufacturing%20environments.pdf